Xilinx AXI Stream tutorial - Part 1

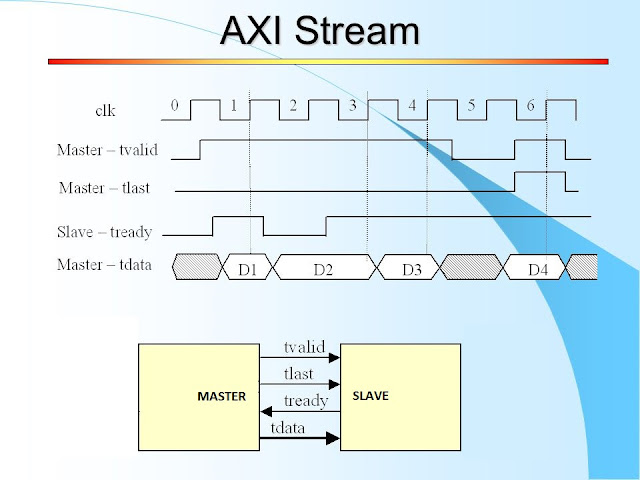

Hi, In this series of articles, I am going to present the design of an AXI4-Stream master. As I often do in my tutorials, I will try to show the design procedure for the block, starting from a “bare bones” solution and gradually adding features to it. Xilinx provides a wide range of AXI peripherals/IPs from which to choose. My purpose in making my own block was to learn the protocol ‘hands-on’. As a side effect, this tutorial provides you with a (synthesizable) AXI4 Stream master which I have not seen provided by Xilinx. The closest IP provided by Xilinx, that I know of, is an AXI memory mapped to AXI stream block. Continue reading...

What about licences issues and available free softwares ?

ReplyDeleteHi,

DeleteThanks for your question. It is a really big one. License covers several aspects, for example, one aspect of the license is wether you can synthesize Verilog or VHDL. Another aspect is your capabilities to simulate. And yet another one, is if mixed languages designs are supported. As a general answer, both major FPGA providers, Intel Altera and Xilinx, provide some form of free access to tools. This free access changes from time to time regarding what features are delivered and which devices are covered. You'd better check in their websites.

Verilog has Verilator and Icarus Verilog, whereas VHDL has NVC and GHDL as free simulators. Generated waveforms can be viewed in GTKwave. With YOSYS, a first free synthesis tool is available for Lattice iCE 40 FPGAs. YOSYS consumes Verilog code by default, but the GHDL project is working on a proof-of-concept for a VHDL frontend for YOSYS.

DeleteMyHDL is not a HLS language. It's HDL in the same RTL level as VHDL/Verilog. The power it brings is related to have a very clear language as basis: Python. Also it really has far devanced testing support from Python core libraries.

ReplyDeleteUnfortunately the comparison misses some important features of VHDL, which do not exist in Verilog and were added in SystemVerilog: This includes Enumeration Types (make Code extremely well readable), Records (can be used to dramatically simplify transaction level interfaces), Assert statements (extremly helpful in debugging).

ReplyDeleteLanguage style for me is secondary. I come from Pascal and therefore prefer the syntax style of VHDL (rather text than symbols), a C programmer may prefer the Verilog look-alike. The additional testbench oriented features of SV require a good understanding of OOP which unfortunately not all HDL designers have..

And about syntax "problems": there are so many language sensitive (free) editors available, that syntax details is definitely no topic anymore!

But as the text says: Both VHDL and Verilog (and also SV) are HDL and at the end you can do all with both languages.

If you are going to bother to do a review, include the latest information - like with VHDL-2008 VHDL is as concise as Verilog or SystemVerilog and with the OSVVM verification library that VHDL is as capable and concise as SystemVerilog + UVM.

ReplyDeleteWe may as well debate Emacs vs. Vi while we're at it :). Both are equally obsolete. Si has evolved to incorporate 25000x(!) more transistors over the lifetime of these languages. The problem is there's been nothing palatable to replace them with. Modeling hardware w/ C++ is absurd. Chisel is interesting, but rather scary to most designers. Fortunately, there's a newcomer -- Transaction-Level Verilog (TL-Verilog) that introduces abstract design constructs without giving up on RTL details. You really need to check it out. It has clean syntax that's easy to learn. I lead the development of makerchip.com where you can learn about and develop in TL-Verilog. Certainly I'm biased, but I assure you, you will never look back to RTL languages again!

ReplyDeleteHi Steve,

DeleteYou may want the last FPGA'er comics strip at http://fpgasite.blogspot.co.il/2017/09/vhdl-arbiters.html