The MicroZed chronicles - free FPGA book

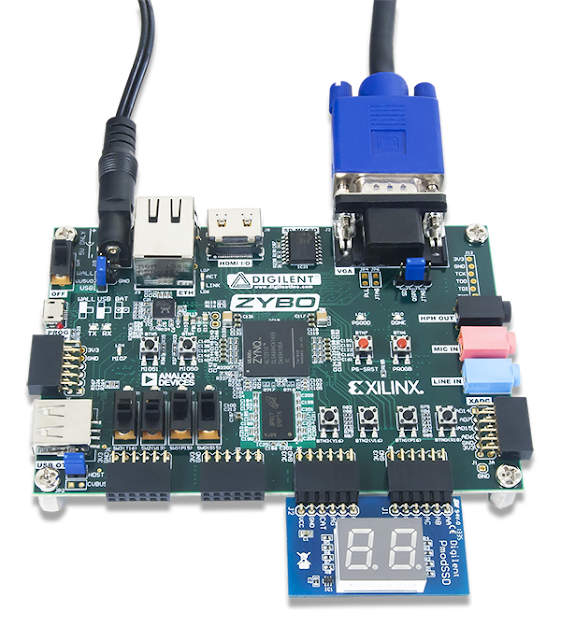

Adam Taylor is the well known author of the MicroZed Chronicles blog on Xilinx website. His Chronicles have been running for several years, and Adam has already compiled entries from his blog in two books. The first book is offered for free on the FPGARelated website for registered users. This is a partial list of the book contents: Introduction to the Zynq Software environment and configuration The Boot loader XADC Multiplexed IO Timers, clocks and watchdogs Processing System and Programmable Logic DMA Adding an Operating System MultiProcessing etc. The book can be find here . Author Adam Taylor is a regular contributor on Xilinx Xcell Daily Blog and he also has his own website .