Popular posts from this blog

Xilinx AXI Stream tutorial - Part 1

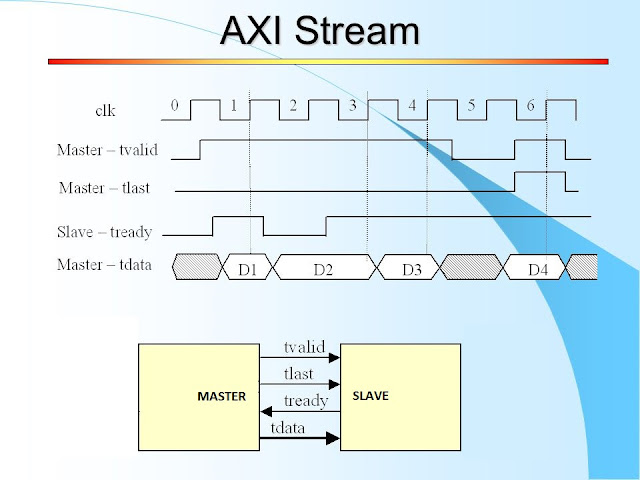

Hi, In this series of articles, I am going to present the design of an AXI4-Stream master. As I often do in my tutorials, I will try to show the design procedure for the block, starting from a “bare bones” solution and gradually adding features to it. Xilinx provides a wide range of AXI peripherals/IPs from which to choose. My purpose in making my own block was to learn the protocol ‘hands-on’. As a side effect, this tutorial provides you with a (synthesizable) AXI4 Stream master which I have not seen provided by Xilinx. The closest IP provided by Xilinx, that I know of, is an AXI memory mapped to AXI stream block. Continue reading...

Comments

Post a Comment