Popular posts from this blog

Xilinx AXI Stream tutorial - Part 1

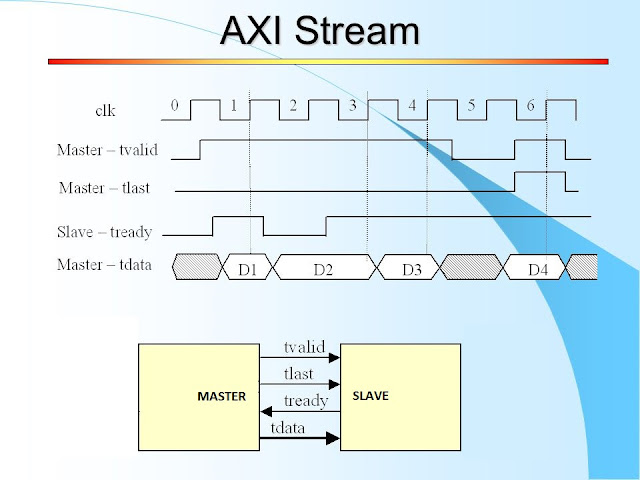

Hi, In this series of articles, I am going to present the design of an AXI4-Stream master. As I often do in my tutorials, I will try to show the design procedure for the block, starting from a “bare bones” solution and gradually adding features to it. Xilinx provides a wide range of AXI peripherals/IPs from which to choose. My purpose in making my own block was to learn the protocol ‘hands-on’. As a side effect, this tutorial provides you with a (synthesizable) AXI4 Stream master which I have not seen provided by Xilinx. The closest IP provided by Xilinx, that I know of, is an AXI memory mapped to AXI stream block. Continue reading...

I designed a compact single bus(control unit arbitrated) processor with a few friends of mine last year , alll worked well at the sumilation level , us forcing the bus to a high impedance state when not being used. We got the shocker the evening when we finished the design as we did our first synthesis run - no tri state buses inside the Atrix 7 Fpga`s , We spent the rest of the night creating seperate input & outputs for each device on the bus and had to introduce a seperate bus arbitrator module. So much for a neat and compact design :P

ReplyDeleteYou can program the project with tristates if it is convinient. And the project will be very well. The fact is that the synthesizer substitutes these tristates to the wires and multiplexer.

ReplyDelete