Xilinx AXI Stream tutorial - Part 1

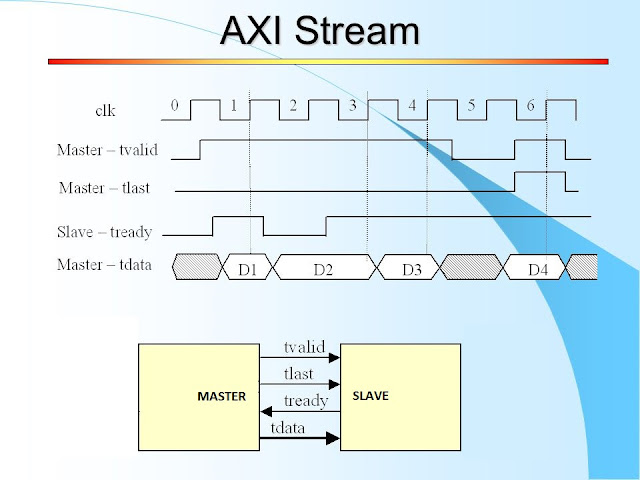

Hi, In this series of articles, I am going to present the design of an AXI4-Stream master. As I often do in my tutorials, I will try to show the design procedure for the block, starting from a “bare bones” solution and gradually adding features to it. Xilinx provides a wide range of AXI peripherals/IPs from which to choose. My purpose in making my own block was to learn the protocol ‘hands-on’. As a side effect, this tutorial provides you with a (synthesizable) AXI4 Stream master which I have not seen provided by Xilinx. The closest IP provided by Xilinx, that I know of, is an AXI memory mapped to AXI stream block. Continue reading...

When is the next chapter available?

ReplyDeleteHi, one year ago I started working with Xilinx FPGAs in (what I thought then) would be a permanent switch in my career. Well, it didn't work, and I am back working with devices I know for many years, namely Altera. Since I don't think I can teach a subject I am not using daily, regretfully I must say I don't see this blog updating any time soon. Thanks for your interest, anyway.

DeleteYou can now teach us about AVALON :)

DeleteHello,

ReplyDeletei think there is something wrong with this implementation since you don't consider the axis_tready signal and though if the slave can't accept data you loose packets ....

The tready signal does not need to be implemented. It is however recommended (see https://developer.arm.com/documentation/ihi0051/a/Default-Signaling-Requirements/Default-value-signaling/Optional-TREADY?lang=en)

Delete